[컴퓨터구조] 정리_2

resilient

·2021. 4. 28. 00:04

중앙 처리장치

CPU

프로세스 는 연산이나 데이터를 처리하기 위해 현재 진행되는 작업이나 프로그램을 의미한다.

프로세서 는 컴퓨터 내부의 처리장치. 컴퓨터 내부에 포함된 하나의 모듈, CPU 칩 혹은 컴퓨터 자체를 의미한다.

CPU의 기능은

명령어와 데이터를 처리하는 일이다.,

프로그램에서 주어진 명령어를 인출해서 해독하고

명령에 따라 데이터를 인출해 연산을 수행하고 그 결과를 저장하거나 다른 장치로 전송한다.

CPU의 기본 구성요소는

연산장치, 레지스터, 제어장치로 구성되어 있다.

연산장치 - 산술 및 논리연산장치

레지스터 - 연산을 위해 다양한 용도로 사용되는 CPU내부의 일시적인 기억장소

제어장치 - 명령을 해석하고 실행하기 위한 제어신호 발생. 연산,읽기 쓰기 등 동작신호와 타이밍신호

마이크로 프로세서

작은 처리장치 라는 뜻으로 반도체 칩에 집적시켜 소형화시킨 CPU 라는 뜻이다.

마이크로프로세서는 컴퓨터 내부에 하나가 아니다.

메인보드에 장착된 가장 강력한 프로세서가 CPU인거고

비디오카드, 사운드 카드등 여러가지 프로세서들이 있다.

마이크로컨트롤러

범용이 아닌, 주로 산업용기기의 제어를 위해 만들어진 특수목적용 마이크로프로세서

주된 형태는 one-chip 마이크로컴퓨터이다.,

몇 비트 컴퓨터인가? 64비트 컴퓨터인가?

- 데이터버스의 비트 수로 계산

CPU 내부와 외부 사이에 한 번에 주고받을 수 있는 데이터버스의 비트 수

- 범용 레지스터의 비트 수로 계산(확실하다)

CPU 내부 범용 레지스터가 정수 연산에서 한 번에 처리할 수 있는 비트 수

64비트 명령어 구조로 설계된 CPU는 32비트로 작성된 프로그램과의 호환성을 고려한 설계를 한다.

보조 프로세서 (혹은, 코프로세서)

협력 처리장치의 합성어이다.

메인 프로세서에 없거나 부족한 기능을 도와 컴퓨터 시스템의 성능을 높여주는 특수목적용 프로세서이다.

보조프로세서의 종류는 사용목적에 따라 나뉜다.

- 부동소수점 처리장치, 그래픽 가속기

- 디지털 신호처리(DSP) 처리

- 암호화 장치 등

부동 소수점 처리장치(FPU)

수치연산 보조 프로세서로 CPU가 범용으로 사용된다.

수치해석, 표 작성, 컴퓨터그래픽, 게임 등 멀티미디어 기능을 처리할 때 빠른 속도를 가진다.

스프레드 시트

표 형태의 양식을 이용해 자동으로 계산하도록 만든 일종의 표 계산 프로그램

부동소수점 연산이 사용되는 대표적인 작업

스프레드시트 소프트웨어

비지칼크 - 세계 최초의 전자식 스프레드시트 소프트웨어

비지칼크 → 로터스 → 엑셀 진화

그래픽 액셀러레이터

그래픽 데이터를 처리하기 위한 전용 보조프로세서

주로 비디오카드에 장착되어 윈도우 운영체제나 멀티미디어 환경에 적합하도록 프로그래밍

그래픽 데이터를 처리하는 CPU의 부담을 경감

- 비트맵 그래픽 - 비트맵 점으로 만든 지도라는 뜻 .jpg .gif .png 축소 확대하면 굵기변하고 계단현상

화면을 사진과 같은 화소로구성

- 벡터 그래픽 - 선과 도형을 좌표, 크기, 방향으로 저장하는 컴퓨터 프로그래밍으로 작성되는 디지털 이미지 - 객체지향 그래픽 .wmf, .emf

화면을 디지털 도형으로 처리

CPU 칩에 내장

FPU와 그래픽처리장치 내장

요즘 CPU프로세서 칩에서는 FPU,GPU, 캐시를 내장하고 있다.

- 싱글 코어 프로세서는 FPU를 코어의 일부로 취급하지않는다.

- 멀티 코어 프로세서는 일부로 취급한다.

CPU코어

- CPU 고유 기능이 이루어지는 핵심 부분

- 프로그램 명령을 읽고 실행하는 단위

- CPU가 단독으로 명령을 실행하는데 필요한 부분

레지스터

❑ 어큐뮬레이터(accumulator, AC) 혹은 누산기

⚫ 연산에 가장 빈번하게 사용, 데이터를 일시 저장

⚫ →연산 결과가 다시 자신에게 누적(accumulation)

❑ 프로그램 카운터(program counter, PC)

⚫ 다음에 인출해올 명령어의 주소를 저장

❑ 메모리 주소 레지스터(memory address register, MAR)

⚫ 주소버스로 주소를 출력하기 전에 임시로 저장

❑ 메모리 버퍼 레지스터(memory buffer register, MBR)

⚫ 데이터버스로 데이터를 읽고 쓸 때 임시로 저장

레지스터의 구성

- 명령 레지스터 - 가장 최근에 인출된 명령어를 저장

- 포인터 - 데이터의 주소를 저장

- 기타 범용 레지스터 - 연산 도중에 일시적인 기억장소로 사용

- 어큐뮬레이터 - 데이터를 주로 저장 AC

- 카운터 - 데이터의 개수를 저장

연산 장치(ALU)

연산장치

수치 데이터에 대한 산술연산과 2진 데이터에 대한 논리연산이 이루어지는 부분

연산장치의 일반적인 구성 요소

- 상태 레지스터 - 최종 실행된 연산결과의 상태를 저장

- 2의 보수화기 - 2의 보수를 생성

- 산술연산장치

- 논리연산장치

- 시프트 레지스터 - shift register → 비트 열 이동

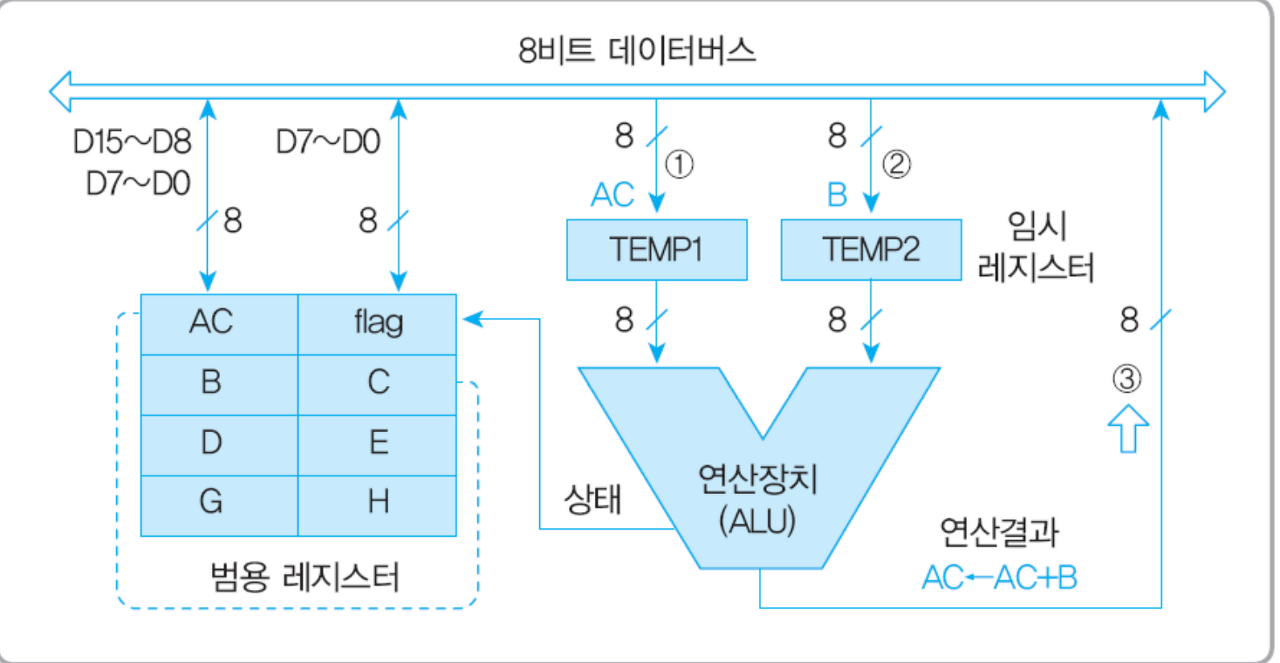

ALU의 동작

누산기를 사용하는 이유

- 연산에서 주로 사용하는 어큐뮬레이터 AC

- 한정된 범용 레지스터의 사용 개수를 줄임

<어셈블리 명령어>

어큐뮬레이터 AC와 다른 범용 레지스터 B에 실린 데이터를 더해 다시 AC로 저장하라는 산술연산

ADD AC,B

AC +B → AC

단일 버스 구조는 3단계 마이크로 연산 필요

- t1 : AC → TEMP1

AC의 내용을 임시 레지스터 TEMP1으로 전송

- t2 : B → TEMP2

- B레지스터의 내용을 임시 레지스터 TEMP2로 전송

- t3 : TEMP1 + TEMP2 → AC

- TEMP1 과 TEMP2 값을 더해 AC로 전송

상태 레지스터

- 혹은 플래그 레지스터

- 연산결과에 따른 연산장치의 상태를 저장

- 조건 분기 명령들

플래그 비트 설계 방법

자신의 조건 상태가 의미를 가질 때 1로 set

- 부호 - 0이면 양수 1이면 음수

- 캐리 - 자리 올림수 , 빌림수 발생하면 set

- 제로 - 연산결과 0 이면 set

- 동등 - 두 수 비교한 결과가 같으면 set

- 오버플로우 - 자릿수가 넘치면 set

- 인터럽트마스크 - 인터럽트 가능이면 0, 불가능으면 1

- 특수권한 - 관리자 모드면 set

CPU명령어

명령어 세트

- 특정 CPU를 위해 정의되는 명령어들 리스트나 집합

- 명령어 세트 구조

- CPU 명령어 세트를 설계할 때에 고려 사항

명령어 형식

주소지정 방식

연산의 종류

데이터 타입

명령어 종류

- 산술연산명령

부호와 정수 부동소수점 고려

- 논리연산 명령

비트 연산 등 각 데이터 단위 간 연산을 고려

- 데이터 처리 및 메모리 연산 명령

데이터의 입출력 로드 저장을 실행

- 흐름제어 연산

프로그램의 실행순서를 바꾸는 명령을 실행

명령어 형식

일반적인 명령어 형식

- 연산코드, 연산자

연산의 동작을 지정, 연산기호 연산의 종류와 방법을 나타내는 동작코드

- 오퍼랜드, 피연산자

연산에 필요한 대상이나 위치를 표시한다.

- ex_ 3+5

연산기호 + 는 연산자

3,5는 피연산자 (연산당하는수)

명령어 형식의 설계

한 명령어 안에 여러개의 오퍼랜드 필드가 가능하다. 오퍼랜드 = 피연산자

① ADD [Y] ; AC ← AC + M[Y]

⚫ AC와 메모리 Y 번지 내용 더해 다시 AC에 저장

❑ ② ADD B, [Y] ; B ← B + M[Y]

⚫ B 레지스터와 메모리 Y 번지 내용 더해 다시 B에 저장

❑ ③ ADD B, C ; B ← B + C

⚫ B, C 레지스터 내용 더해 다시 B 레지스터에 저장

❑ ④ ADD B, C, D ; B ← C + D

⚫ C, D 레지스터 내용 더해 B 레지스터에 저장

어드레싱 모드 (주소지정방식)

- 명령어 형식에 포함된 오퍼랜드 필드에서 실제 피연산자를 찾아내는 방법

- 명령어 길이의 비트 수 제약에서 벗어나 더 큰 기억용량이나 더 큰 단위의 데이터를 처리

- 유효주소와 간접주소의 개념

유효주소 - 실제 오퍼랜드의 주소, 실제 피연산자가 저장된 메모리 위치

간접주소 - 유효주소가 저장된 메모리 위치

주소지정 방식의 종류와 명령어 설계(가상)

<어셈블리 명령어 ; 레지스터 전송언어> 로 표시

- 산술연산 INC,ADD AC, PC, B,C IX, d

- 암시적 주소지정 방식ex) INC ; AC ← AC + 1

오퍼랜드 없이 연산코드 자신만으로 특정 레지스터의 동작을 암시, AC의 비트 증가, 감소, 반전 같은 연산

- 즉시 주소지정 방식 ex) ADD B, 90H ; B ← B + 90H

명령어 형식의 오퍼랜드 필드에 <즉시 사용할 수 있는 데이터 수치> 로 실제 피연산자가 들어 있음

- 직접 주소지정 방식 ex) ADD B, [1234H] ; B ← B + M[1234H]

오퍼랜드 필드에 실제 피연산자가 저장된 메모리 위치인 유효주소가 들어있다.

- 간접 주소지정 방식 ex) ADD B, [ [5678H] ] ; B ← B + M[ M[5678H] ]

오퍼랜드 필드에 유효주소가 저장된 메모리 위치인 간접주소가 들어있음

- 레지스터 주소지정 방식 ex) ADD B, C ; B ← B + C

오퍼랜드 필드에서 지정한 레지스터에 실제 피연산자

- 레지스터 간접 주소 지정 방식 ex) ADD B, [C] ; B ← B + M[C]

오퍼랜드 필드에서 지정한 레지스터에 유효주소 저장

- 상대 주소지정 방식 ex) ADD B, [PC+d] ; B ← B + M[PC+d]

오퍼랜드 필드에서 지정한 프로그램 카운터 PC에 저장된 주소 값과 변위 값 d를 더해 유효주소 계산

- 인덱스 주소지정 방식 ex) ADD B, [IX+d] ; B ← B + M[IX+d]

상대 주소지정 방식의 일종

지수 바이어스

2진 부동소수점 형식에서 지수에 일정기준 값을 더해 지수부를 부호가 필요없는 영역으로 옮겨 저장

→ 부호를 갖는 지수를 2의 보수로 표현하면 두 수의 크기를 비교하기 어렵기 때문

IEEE 754 표준에서 지수부 값

지수부가 k비트 → (2*(k-1)-1) 바이어스 된 지수로 저장

정규화 형식

부동소수점 수식 표현은 같은 수라도 소수점 위치에 따라 여러 가지로 표현되므로 혼동됨

논리 및 시프트 연산

→ALU 장치의 논리연산

- 논리연산은 컴퓨터 워드가 서로 대응하는 비트 위치끼리 주로 비트 단위로 데이터 연산

- 기본적인 논리연산 사용

- 시프트 레지스터를 이용한 비트 열 이동으로 다양한 시프트 연산 수행

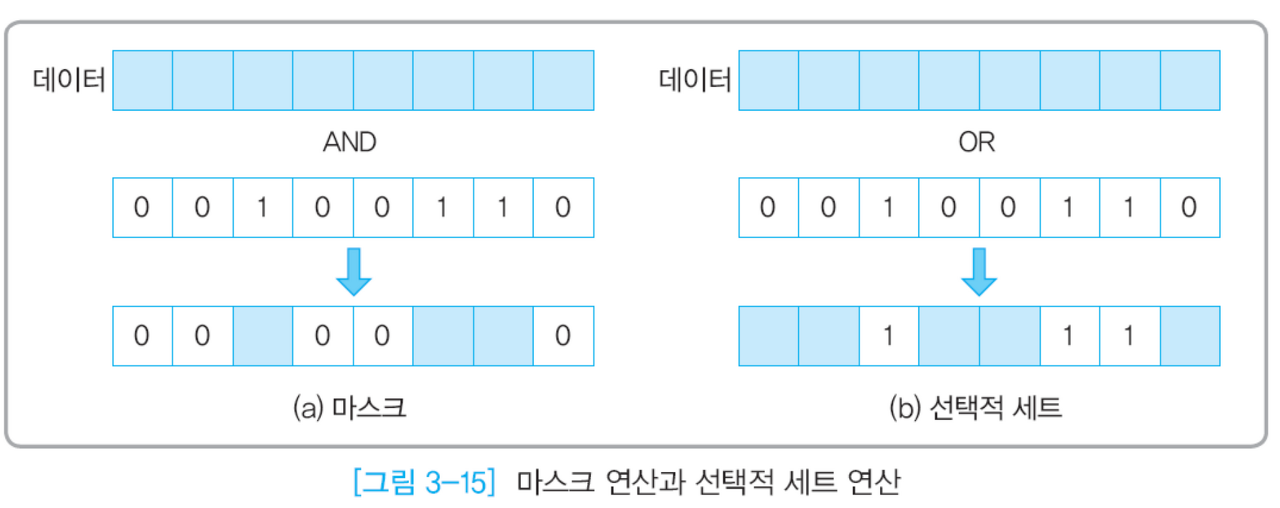

논리연산의 응용

- 마스크 연산 - AND 연산으로 원하는 위치의 비트만 통과

- 선택적 세트 연산 - OR 연산으로 원하는 위치의 비트만 1로 set

- 삽입 연산 - AND 연산으로 원치 않는 위치의 비트를 지우고 OR연산으로 다른 데이터 값으로 교체

- 비교연산 - XOR으로 다른 값을 갖는 위치의 비트만 1로 찾음

- 선택적 보수 연산 - XOR 연산으로 원하는 위치의 비트만 1의 보수로

시프트 연산

논리적 시프트 연산

- 부호를 고려하지 않음

- 시프트 레지스터 비트들이 좌우로 1비트씩 이동

- 곱셈이나 나눗셈등에 적용

순환 시프트 연산

- 부호를 고려하지 않음

- 부호 비트를 포함해 시프트 레지스터의 비트들이 좌우로 회전해 다시 반대쪽 입력으로 들어감

- 직렬 데이터의 비트 전송에 사용

산술적 시프트 연산

- 부호 비트를 제외한 나머지 비트들이 좌우로 이동

- 2의 보수 표현에서 산술적 우측 시프트는 부호 비트가 우측으로 복사됨

'CS & Network > 운영체제(OS) & 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] 메모리 (0) | 2021.05.05 |

|---|---|

| [컴퓨터구조] 기억장치 (0) | 2021.05.03 |

| [컴퓨터구조] 파이프라인 (0) | 2021.05.01 |

| [컴퓨터구조] 정리_3 (0) | 2021.04.29 |

| [컴퓨터구조] 정리_1 (0) | 2021.04.26 |